# Power- and Performance-aware On-Chip Interconnection Architectures for Many-core Systems

by

### Hemanta Kumar Mondal

Under the Supervision of Dr. Sujay Deb

Indraprastha Institute of Information Technology Delhi

April, 2017

© Indraprastha Institute of Information Technology Delhi (IIITD),

New Delhi 110020

# Power- and Performance-aware On-Chip Interconnection Architectures for Many-core Systems

by

### Hemanta Kumar Mondal

#### Submitted

in partial fulfillment of the requirements for the degree of Doctor of Philosophy

to the

Indraprastha Institute of Information Technology Delhi

April, 2017

Certificate

This is to certify that the thesis titled "Power- and Performance-aware On-Chip

Interconnection Architectures for Many-core Systems" being submitted by Mr.

Hemanta Kumar Mondal to the Indraprastha Institute of Information Technology Delhi,

for the award of the degree of Doctor of Philosophy, is an original research work carried

out by him under my supervision. In my opinion, the thesis has reached the standards

fulfilling the requirements of the regulations relating to the degree.

The results contained in this thesis have not been submitted in part or full to any other

university or institute for the award of any degree/diploma.

April, 2017

Dr. Sujay Deb

Indraprastha Institute of Information Technology Delhi

New Delhi 110 020

i

Dedicated to the loving memories of my Father and my Uncle.....

### Acknowledgements

I have been indeed lucky to have the opportunity to work with Dr. Sujay Deb, my PhD advisor. It would not be possible to complete this journey without his immense supports. He always guided me not only as a mentor, But also as a great philosopher. I learned a lot under his supervision. Dr. Deb is one of the most fascinating people I have ever met in my life. His enthusiasm, excellent insights, strong technical expertise, and systematic problem solving approach helped me a lot to excel my research career. His immense energy, optimism and positive attitude have kept on motivating me to face the challenges both at professional and personal level. Thank you, Dr. Sujay Deb. I am looking forward to continue research with you in future.

A special mention for my doctoral committee members Dr. M. S. Hashmi and Dr. Alexander Fell and my collaborator Dr. Amlan Ganguly, who have played a major role in shaping my PhD journey. I thank them for their insightful feedback and comments. I would take the privilege to acknowledge Prof. Pankaj Jalote for his thought and research vision which I really admire. A Special Thanks to all Professors and all Administrative Staffs for all kinds of financial and infrastructure support. Specially, I would like to thank Mr. Ashutosh Brahma for his ample support throughout my PhD journey. In every difficult time, he was always with me.

I would like to thank all my (present and past) colleagues Naushad Ansari, Shiju S, Dr. Hemant Aggarwal, Wazir Singh, Vijay Sharma, Naveen Gupta, Salin Verma. Rakhi Hemani, Sonal Aggarwal, Ayushi Rastogi, Aijaz Zaidi, Amit Chauhan, Rahul Gangopadhyay, Dinesh Rano, Deepayan Banerjee, Nalla Anandakumar, Mitali Sinha, Arpan Jati, Dipto Sarkar, Nilabha Bhattacharjee and Aritra Hazra for their presence during my tough time. I would like to show my sincere thanks to all lab mates for their support, valuable technical discussions and specially, 'Friday party' which I would miss it a lot. It would be my pleasure to extend my gratitude to Sri Harsha Gade, Raghav Kishore, Wazir Singh, Sidhartha Sankar Rout and Shashwat Kaushik for their massive supports during my research.

My family's support has been enormous throughout my journey. Biggest thanks to my father, mother, uncle, aunty, sisters, and brothers, and all my relatives for their remarkable supports. Thank you all once again for constant support and blessings throughout my journey. Thanks to my wife- Mampi. She never forced me to bring her to University. Thanks god that I got such a wonderful wife. Now, it's time to start second phase of my life. Thank you all!!!

### **Abstract**

Networks-on-Chip (NoCs) are fast becoming the de-facto communication infrastructures in Chip Multi-Processors (CMPs) for large-scale applications. The traditional approaches of implementing a NoC with planar metal interconnects have high latency and significant power consumption overhead. This is mainly due to the multi-hop data exchange using wired links, specifically when the number of cores is significantly high. To address these problems, Wireless NoCs (WNoCs) that augment multi-hop wired interconnects in a NoC with high-bandwidth, single-hop, long-range wireless links are being explored. Although multi-hop communication is replaced by WNoC, still, NoC components including wireless transceivers consume a significant portion of chip power, which is one of the major bottlenecks in NoC architectures for CMPs. With progressing generations and system sizes, this proportion increases exponentially. Another important concern with the existing WNoCs is the performance limitations due to single frequency channel communication with omnidirectional antenna setups. These bottlenecks open up new opportunities for detailed investigations into the power and performance efficiency of WNoCs and design low-energy, high-performance communication infrastructures for CMPs.

Analysis of network resources for several benchmarks shows that, utilization and hence energy consumption is application dependent and the desired performance can be achieved even without operating all resources at maximum specifications. To reduce the power consumption, we propose a leakage power-aware NoC architecture using power gated router based on the router utilization. To compute the utilization of routers, we propose an adaptive two-step estimation method that computes utilization at both global and local router levels. This hybrid estimation method provides an accurate prediction of router utilization with low run-time overheads. Using the utilization estimates, we reduce the switching and idle-state power consumption of WNoC architecture. To eliminate power-gating impacts and maintain the performance, we implement a deadlock-free Seamless Bypass Routing (SBR) strategy that bypasses a power-gated router.

Based on the utilization of routers, we propose a switching (dynamic) power-aware NoC architecture using Adaptive Multi-Voltage Scaling (AMS) mechanism to achieve significant energy saving. To implement the AMS based WNoC architectures, we also propose a multi-level voltage shifter along with efficient control mechanism that allows switching between two voltage levels from a given fixed set of voltage levels. But most wireless interconnects are implemented using a token passing protocol in which only a single paired is actively involved in data transmission at any given time. Hence, the

wireless transceivers can be selectively switched on and off depending on the workload. This will improve the power efficiency of the network without affecting the overall network performance, especially when all the wireless transceivers are designed to operate at the same frequency and only one pair can use the channel at a time.

Since all these wireless links are not required all time, power-gated wireless transceivers can provide an effective solution for power efficient WNoC design. In this dissertation, to increase the power efficiency, we also propose the partially power gated transceiver for wireless interfaces (WIs) using AMS to reduce the idle-state power consumption based on the utilization of WIs. For packets transmitted over wireless links, receiver-end control strategy is proposed with WNoC. This enables effective power gating strategy for WIs as it eliminates periodic waking up of complete receiver chain. The proposed technique also reduces routing overhead and need of control signals significantly.

However, most existing WNoC architectures generally use omnidirectional antenna along with token passing protocol to access wireless medium. That limits the achievable performance benefits since only one wireless pair can communicate at a time. It is also not practical in the immediate future to arbitrarily scale up the number of non-overlapping channels by designing mm-wave transceivers operating in disjoint frequency bands. Consequently, we explore the use of directional antennas where multiple simultaneous wireless interconnect pairs can communicate. Concurrent wireless communications can result in interference. This can be minimized by optimal placement of wireless nodes. To address this, we propose an interference-aware Directional Wireless NoC (DWNoC) topology with optimal placement of WIs by incorporating planner log-periodic antennas (PLPAs). This DWNoC architecture enables the directional point-to-point links between transceivers and hence multiple wireless links can operate at the same time without interference. It also increases the energy efficiency of DWNoC as well as utilization of WIs significantly as compared to existing NoC architectures.

In addition, we also address the on-chip communication bottlenecks between Last Level Caches (LLCs) and Memory Controllers (MCs) to access off-chip memory. Communication between LLCs and memory controllers faces significant challenge due to the placement of memory controllers, high network latency, and switching strategy. Especially, as system size increases, the latency between caches and limited number of memory controllers increases, thereby degrading the memory performance. To overcome this, we propose an adaptive hybrid switching strategy with dual crossbar router to provide low latency paths between caches and memory controllers. The performance is further improved by finding the optimal number and placement of memory controllers with low overheads. To reduce the energy overhead of dual crossbar routers, we introduce partially drowsy and power gated techniques with routers in the proposed architecture.

### **Publications**

#### **Journal Articles**

Hemanta Kumar Mondal, Sri Harsha Gade, M S Shamim, Sujay Deb, and Amlan Ganguly, "Interference-Aware Wireless Network-on-Chip Architecture using Directional Antennas," IEEE Transactions of Multi-Scale Computing Systems (TMSCS), July 2016.

(DOI: 10.1109/TMSCS.2016.2595527)

- 2. **Hemanta Kumar Mondal**, Sri Harsha Gade, Raghav Kishore, and Sujay Deb, "SNoC: Utilization-based Adaptive Strategy for Power-efficient NoC Architecture,". Sustainable Computing, Informatics and Systems Journal, Elsevier. (Minor revision)

- 3. **Hemanta Kumar Mondal**, Sri Harsha Gade, Raghav Kishore, and Sujay Deb, "Adaptive Multi-Voltage Scaling with Utilization Prediction for Energy-efficient Wireless NoC,". IEEE Transactions on Sustainable Computing (**T-SUSC**), August 2017. (Accepted)

- 4. **Hemanta Kumar Mondal**, Sri Harsha Gade, Raghav Kishore, and Sujay Deb, "An Efficient and Reconfigurable Evaluation Framework for Irregular NoC Architecture," (Under preparation)

- Hemanta Kumar Mondal, Sri Harsha Gade, and Sujay Deb,

"Interconnection Supports for Energy-efficient High Bandwidth Memory Access in CMPs," (Under review)

#### **Conference Articles**

- Shrestha Bansal, Hemanta Kumar Mondal, Sri Harsha Gade and Sujay Deb, "Energy-efficient NoC Router for High Throughput Applications in Many-core GPUs." iNIS 2017. (Under review)

- Shashwat Kaushik, Muni Aggarwal, Hemanta Kumar Mondal, Sri Harsha Gade and Sujay Deb, "Path Loss-aware Adaptive Transmission Power Control Scheme for Energy-efficient Wireless NoC", MWSCAS. (Accepted)

- 3. **Hemanta Kumar Mondal**, Shashwat Kaushik, Sri Harsha Gade, and Sujay Deb, "Energy-efficient Transceiver for Wireless NoC," 30th International Conference on VLSI Design (**VLSID**), Hyderabad, January 2017.

- Raghav Kishore, Hemanta Kumar Mondal and Sujay Deb, "Energyefficient Reconfigurable Framework for Evaluating Hybrid NoCs," 20<sup>th</sup>

international symposium on VLSI Design and Test (VDAT), IIT Guwahati,

India, May 2016.

- 5. **Hemanta Kumar Mondal**, Sri Harsha Gade, Raghav Kishore, and Sujay Deb, "Adaptive multi-voltage scaling in wireless NoC for high performance low power applications," Design, Automation & Test in Europe Conference & Exhibition (**DATE**), Dresden, Germany, pp. 1315-1320, 2016.

- Hemanta Kumar Mondal, Sri Harsha Gade, Raghav Kishore, Shashwat Kaushik and Sujay Deb, "Power Efficient Router Architecture for Wireless Network-on-Chip," 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, March 2016.

- 7. **Hemanta Kumar Mondal**, Sri Harsha Gade, Raghav Kishore, and Sujay Deb, "Power- and performance-aware fine-grained reconfigurable router architecture for NoC," Green Computing Conference and Sustainable Computing Conference (**IGSC**), 2015 Sixth International, Las Vegas, NV, pp. 1-6, 2015.

- 8. Sri Harsha Gade, **Hemanta Kumar Mondal**, and Sujay Deb, "A Hardware and Thermal Analysis of DVFS in a Multi-core System with Hybrid WNoC Architecture," 2015 28th International Conference on VLSI Design (**VLSID**), Bangalore, pp. 117-122, 2015.

- 9. **Hemanta Kumar Mondal**, and Sujay Deb, "Wireless network-on-chip: a new era in multi-core chip design," 2014 25nd IEEE International Symposium on Rapid System Prototyping (**RSP**) in conjunction with ESWeek'14, New Delhi, pp. 59-64, 2014. (Invited paper)

- 10. Hemanta Kumar Mondal, and Sujay Deb, "An energy efficient wireless Network-on-Chip using power-gated transceivers," 2014 27th IEEE International System-on-Chip Conference (SOCC), Las Vegas, pp. 243-

248, 2014.

- 11. **Hemanta Kumar Mondal**, Sri Harsha Gade and Sujay Deb, "An Efficient Hardware Implementation of DVFS in Multi-core System with Wireless Network-on-Chip," 2014 IEEE Computer Society Annual Symposium on VLSI (**ISVLSI**), Tampa, FL, pp. 184-189, 2014.

- 12. **Hemanta Kumar Mondal**, and Sujay Deb, "Energy efficient on-chip wireless interconnects with sleepy transceivers," 2013 8th IEEE Design and Test Symposium (**IDT**), Marrakesh, pp. 1-6, 2013.

# Contents

| CERTIFICATE                             | I    |

|-----------------------------------------|------|

| ACKNOWLEDGEMENTS                        | III  |

| ABSTRACT                                | IV   |

| PUBLICATIONS                            | VI   |

| CONTENTS                                | IX   |

| LIST OF FIGURES                         | XIII |

| LIST OF TABLES                          | XVI  |

| CHAPTER 1 INTRODUCTION                  | 1    |

| 1.1 Motivation and Introduction         | 1    |

| 1.2 Contributions                       | 8    |

| 1.2 Dissertation outline                | 11   |

| CHAPTER 2 LEAKAGE POWER-AWARE NOC       | 13   |

| 2.1 Related work                        | 14   |

| 2.2 Leakage Power-Aware NoC             | 16   |

| 2.2.1 NoC Router Design                 | 16   |

| 2.2.2 Global Utilization Computation    | 18   |

| 2.2.3 Runtime Utilization Estimation    | 19   |

| 2.2.4 Power Management Controller (PMC) | 20   |

| 2.2.5 Routing Strategy                  | 22   |

| 2.3 Walkthrough Example                 | 26   |

| 2.4 Performance Evaluation              | 29   |

| 2.4.1 Simulation Setup                          | 29 |

|-------------------------------------------------|----|

| 2.4.2 Performance Metrics Review                | 30 |

| 2.4.3 Router-level Statistics                   | 32 |

| 2.4.4 Bandwidth and Latency Analysis            | 33 |

| 2.4.5 Energy saving                             | 34 |

| 2.4.6 Comparison with Other Low Power NoCs      | 35 |

| 2.4.7 Router Power and Area Overhead            | 36 |

| 2.4.8 Scalability                               | 37 |

| 2.5 Conclusions                                 | 38 |

| CHAPTER 3 SWITCHING POWER-AWARE NOC             | 39 |

| 3.1 Preliminaries and Related Works             | 40 |

| 3.2 Switching and Idle-state Power-aware WNoC   | 42 |

| 3.2.1 System Architecture                       | 42 |

| 3.2.2 Dynamic Runtime Utilization Computation   | 43 |

| 3.2.3 AMS: Base Router Control                  | 46 |

| 3.2.4 AMS: WI Control                           | 48 |

| 3.2.5 Routing Strategy                          | 52 |

| 3.3 Hardware Implementation                     | 52 |

| 3.3.1 Adaptive Multi-Voltage Scaling Controller | 52 |

| 3.3.2 On-Chip Voltage Regulator                 | 53 |

| 3.3.3 Voltage Level Shifter                     | 54 |

| 3.4 Experiments                                 | 56 |

| 3.4.1 Experimental Setup                        | 57 |

| 3.4.2 AMSC-based Router Implementation          | 57 |

| 3.4.3 Power Gated LNA and PA Implementation     | 58 |

| 3.4.4 Comparison of Energy and Energy-delay Product     | 61    |

|---------------------------------------------------------|-------|

| 3.4.5 Energy Saving                                     | 63    |

| 3.4.6 Performance Evaluation                            | 64    |

| 3.4.7 Scalability and Impact of Power Gating            | 66    |

| 3.5 Conclusion                                          | 68    |

| CHAPTER 4 DIRECTIONAL WIRELESS NOC ARCHITECTURE         | 69    |

| 4.1 Related work                                        | 70    |

| 4.2 Communication Infrastructure                        | 72    |

| 4.2.1 Physical Layer Design                             | 72    |

| 4.2.2 Topology of the DWNoC                             | 75    |

| 4.2.3 Interference Aware WI Placement Problem           | 76    |

| 4.2.4 Interference Avoidance Constraints                | 79    |

| 4.2.5 Proposed Optimization Algorithm                   | 80    |

| 4.2.6 Communication Protocol                            | 83    |

| 4.3 Experimental Results                                | 84    |

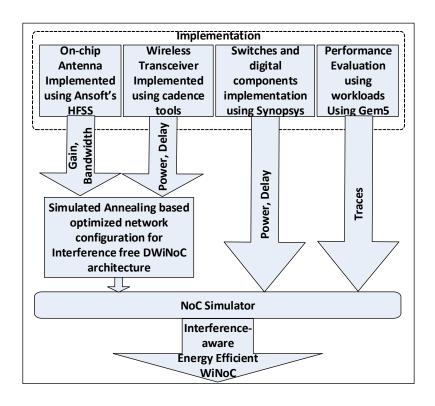

| 4.3.1 Simulation Setup                                  | 84    |

| 4.3.2 Interference-Aware Constraints for WI placement   | 86    |

| 4.3.3 Antenna Characteristics and Link Budget Analysis  | 86    |

| 4.3.4 Interference-Aware WI Placement                   | 92    |

| 4.3.5 Performance Evaluation of DWNoC                   | 92    |

| 4.3.6 Application Specific Traffic                      | 95    |

| 4.3.7 Area Overheads and Scalability                    | 96    |

| 4.4 Conclusion                                          | 97    |

| CHAPTER 5 LOW LATENCY NETWORK FOR OFF-CHIP MEMORY ACCES | S 99  |

| 5.1 Related work                                        | . 101 |

| 5.2 Efficient Low Latency NoC                                       |

|---------------------------------------------------------------------|

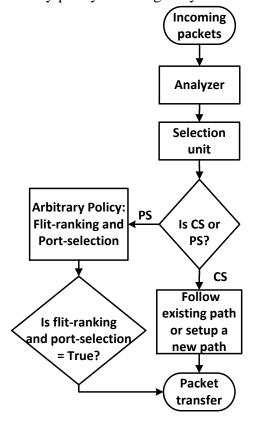

| 5.2.1 Hybrid Switching Strategy                                     |

| 5.2.2 Energy-efficiency                                             |

| 5.3 Experimental Results                                            |

| 5.3.1 Simulation Setup                                              |

| 5.3.2 Router Implementation with Hybrid Switching and Overheads 110 |

| 5.3.3 Memory Controller Placement                                   |

| 5.3.4 Performance Evaluation                                        |

| 5.3.5 Energy saving                                                 |

| 5.3.6. Summary of Existing and Proposed Architectures               |

| 5.4 Conclusions and Future Works                                    |

| 5.4.1 Conclusions                                                   |

| 5.4.2 Future Works                                                  |

| CHAPTER 6 CONCLUSIONS AND FUTURE WORKS                              |

| 6.1 Conclusions 117                                                 |

| 6.2 Future works                                                    |

| 6.2.1 Energy-efficient High Bandwidth Memory Access                 |

| 6.2.2 Hybrid electrical-optical interconnect                        |

| 6.2.3 Fault-tolerant and reliable emerging interconnect             |

| 6.2.4 Network-on-chip architecture for artificial neural networks   |

| BIBLIOGRAPHY122                                                     |

# List of Figures

| Figure 1.1 Normalized NoC power consumption with processing cores at different             |

|--------------------------------------------------------------------------------------------|

| technology nodes                                                                           |

| Figure 1.2 Component wise power consumption of transceiver at 65nm 5                       |

| Figure 1.3 Dynamic and leakage power of router at Vdd=1V                                   |

| Figure 1.4 Overview of energy-efficient WNoC highlighting all the Contributions 9          |

| Figure 2.1 Implementation of power gated hybrid router design for proposed NoC 17          |

| Figure 2.2 Categorization of routers based on pre-computed global utilization under real   |

| applications for a 64-core system                                                          |

| Figure 2.3 Block level diagram shows power management controller with control signals      |

| 21                                                                                         |

| Figure 2.4 Router bypasses links and control circuitry                                     |

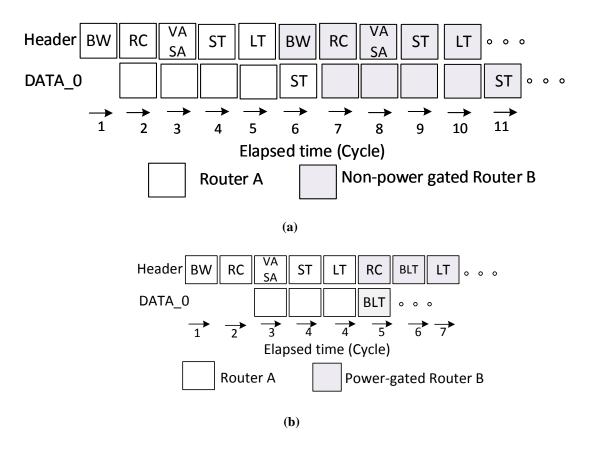

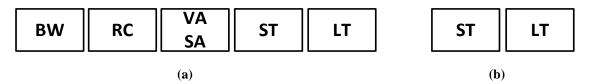

| Figure 2.5 Pipeline stages of (a) regular XY routing and (b) seamless bypass routing 24    |

| Figure 2.6 Example scenario illustrating our proposed architecture                         |

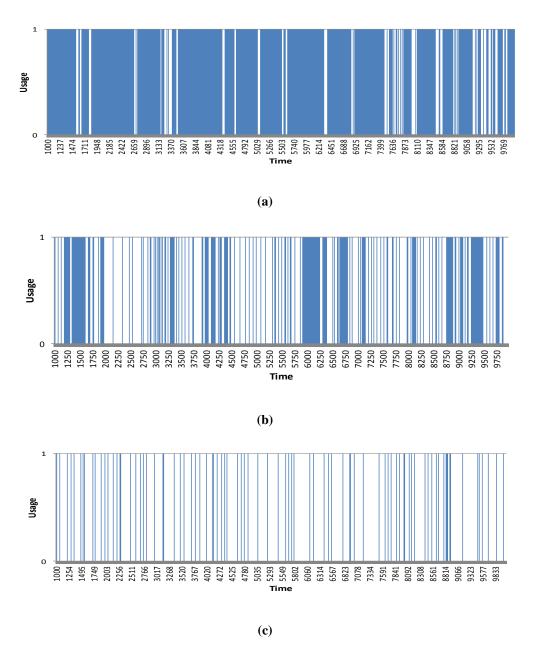

| Figure 2.7 Histogram for flit arrival at router that represents (a) HU, (b) MU and (c) RU  |

| 31                                                                                         |

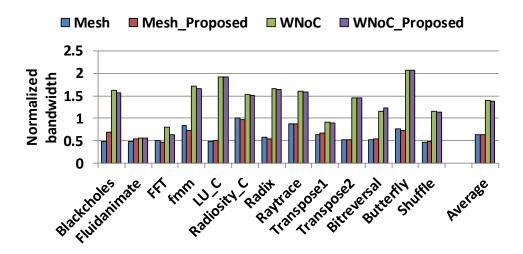

| Figure 2.8 Normalized bandwidth of NoC architectures with different traffic situations for |

| a 64 core system wrt mesh                                                                  |

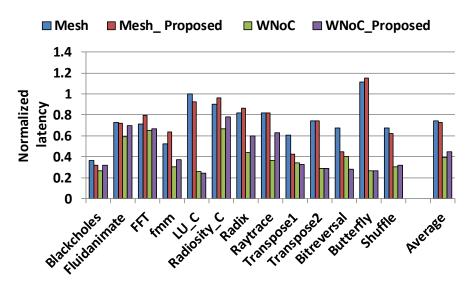

| Figure 2.9 Normalized saturation latency of Proposed NoC based architecture over regular   |

| architectures wrt mesh                                                                     |

| Figure 2.10 Percentage of packet energy saving using proposed NoC over regular mesh        |

| and WNoC                                                                                   |

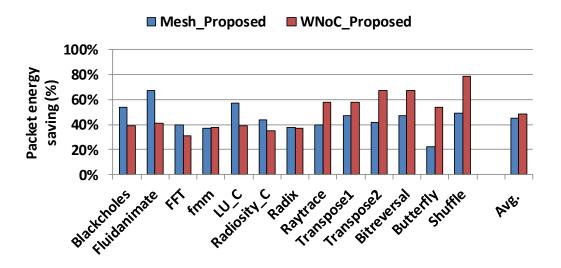

| Figure 3.1 Cluster-level AMS base wireless NoC architecture                                |

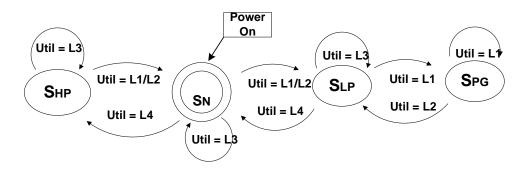

| Figure 3.2 State machine diagram of AMS controller                                         |

| Figure 3.3 Schematic of power-gated LNA and PA with AMSC                                   |

| Figure 3.4 Format of data transmission over wireless link                        | 50        |

|----------------------------------------------------------------------------------|-----------|

| Figure 3.5 Hybrid switched inductor and switched capacitor voltage regulator for | or multi- |

| voltage scaling                                                                  | 53        |

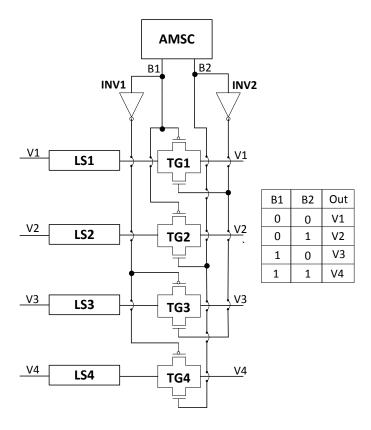

| Figure 3.6 Level shifter with AMSC                                               | 55        |

| Figure 3.7 Level shifter controlling mechanism                                   | 56        |

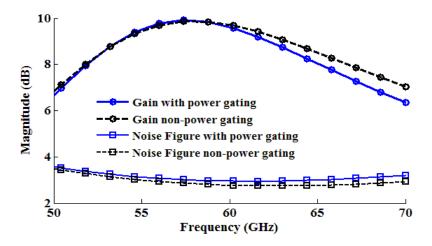

| Figure 3.8 Gain and noise figure analysis for pgLNA and npgLNA                   | 59        |

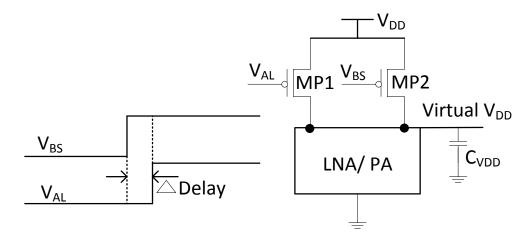

| Figure 3.9 PMOS switches with block level LNA/PA                                 | 59        |

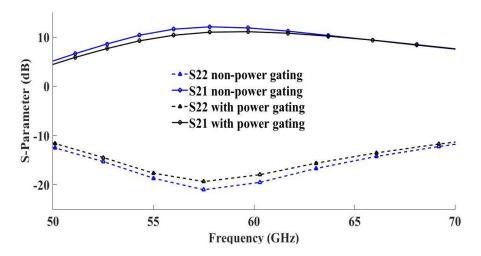

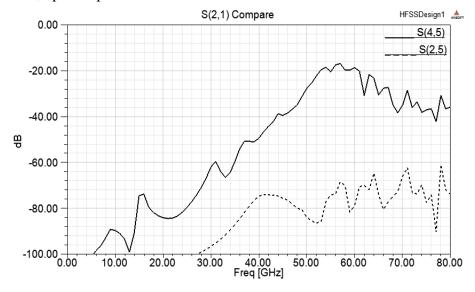

| Figure 3.10 S-parameter analysis for pgPA and npgPA                              | 60        |

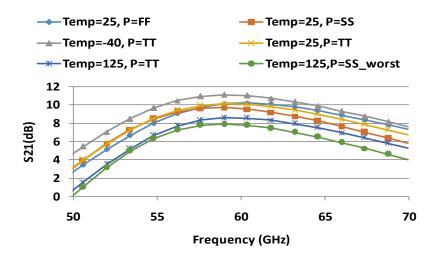

| Figure 3.11 S-parameter analysis across the process and temperature variations   | 61        |

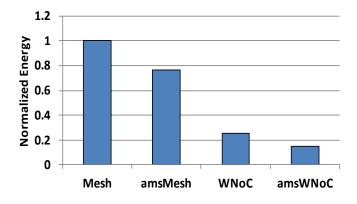

| Figure 3.12 Shows normalized energy of 64 core system under uniform random       | n traffic |

| pattern with respect to baseline Mesh topology                                   | 61        |

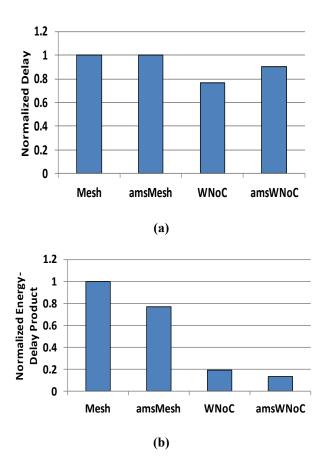

| Figure 3.13 Shows (a) normalized delay and (b) normalized energy-delay produ     | ict of 64 |

| core system under uniform random traffic pattern with respect to baseline Mesh t | opology.  |

|                                                                                  | 62        |

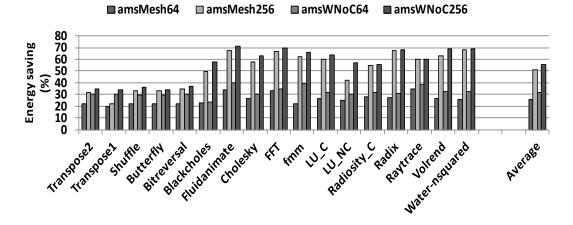

| Figure 3.14 Packet energy saving in percentage with AMS over non-AMS arc         | hitecture |

| under application-specific and synthetic traffic                                 | 63        |

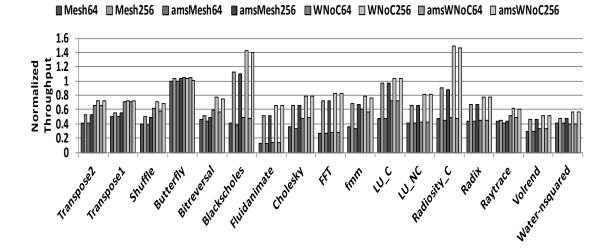

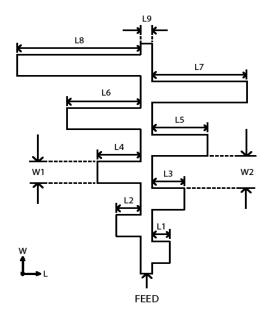

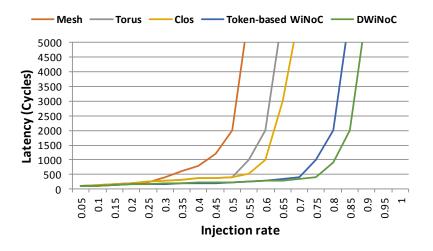

| Figure 3.15 Peak throughput for proposed and baseline architectures              | 65        |

| Figure 3.16 Peak latency for proposed and baseline architectures                 | 66        |

| Figure 3.17 Power consumption of PA/LNA in different operating modes             | 67        |

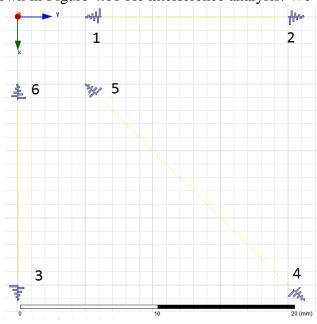

| Figure 4.1 On-chip planar log-periodic antenna with dimensions in mm             | 73        |

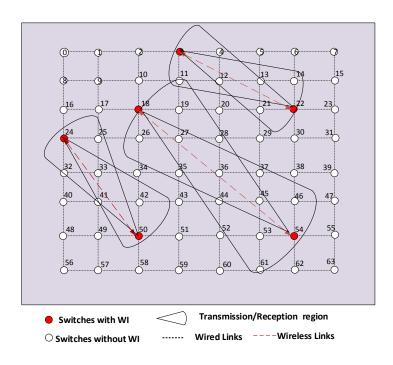

| Figure 4.2 A hybrid hierarchical NoC architecture with subnets structure         | 74        |

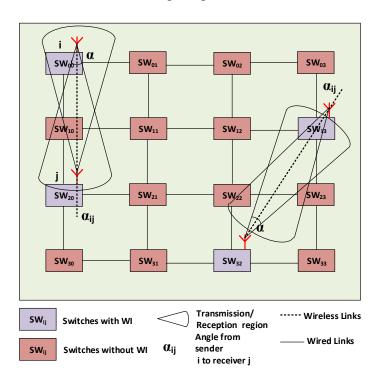

| Figure 4.3 4×4 small world network topology with directional antennas            | 75        |

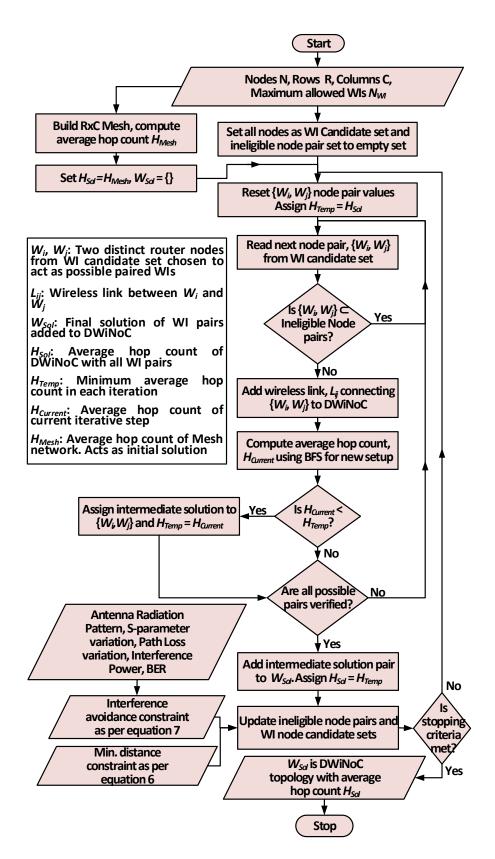

| Figure 4.4 Interference-aware wireless interfaces placement algorithm            | 82        |

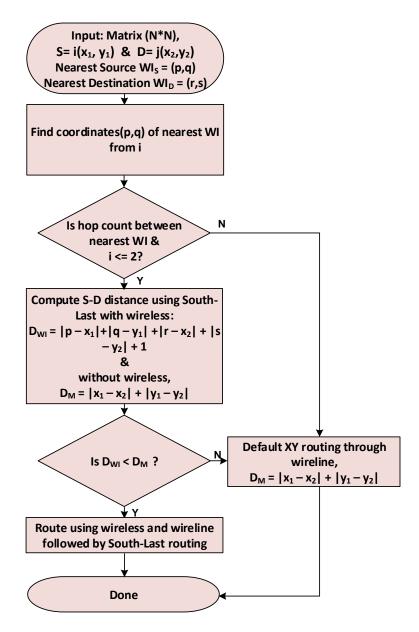

| Figure 4.5 Data routing strategy                                                 | 83        |

| Figure 4.6 Performance evaluation setup for DWNoC                                | 85        |

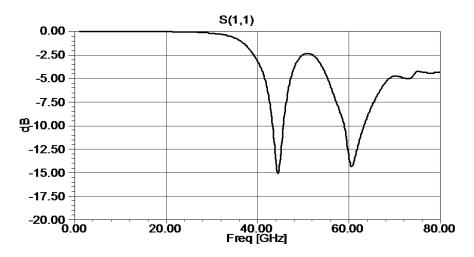

| Figure 4.7 Return loss of the on-chip planar log-periodic antenna                | 87        |

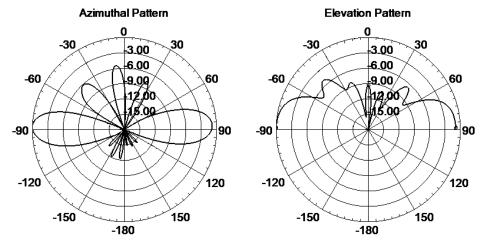

| Figure 4.8 Radiation pattern along the azimuthal and elevation plane             | 87        |

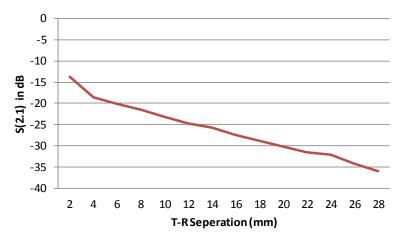

| Figure 4.9 S(2,1) variation with distance                                        | 88        |

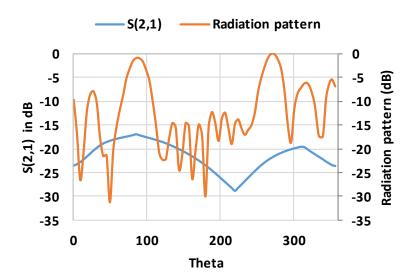

| Figure 4.10 S(2,1) variation with different antenna orientation                  | 90        |

| Figure 4.11 Antennas setup with a different orientation                          | 90        |

| Figure 4.12 S(2,1) plot for SIR calculation.                                     | 91        |

| Figure 4.13 Wireless links placement in 64 core system                              | 92           |

|-------------------------------------------------------------------------------------|--------------|

| Figure 4.14 Latency for various NoC architectures for 64 core system                | 93           |

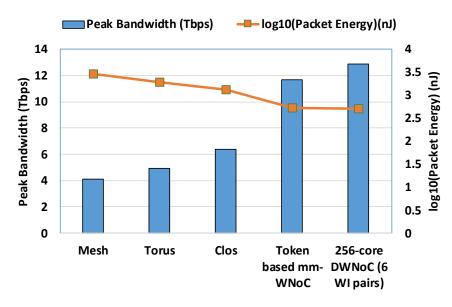

| Figure 4.16 Peak bandwidth and packet energy dissipation of various NoC ar          |              |

| for 256-core system                                                                 | 94           |

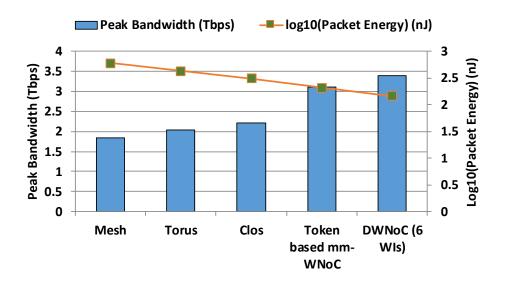

| Figure 4.15 Peak bandwidth and packet energy dissipation of various NoC ar          | chitectures  |

| for 64-core system.                                                                 | 94           |

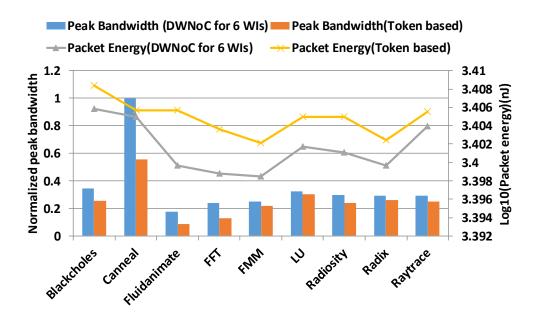

| Figure 4.17 Bandwidth and packet energy of WNoCs with application-specific          | traffic for  |

| 64 core system                                                                      | 96           |

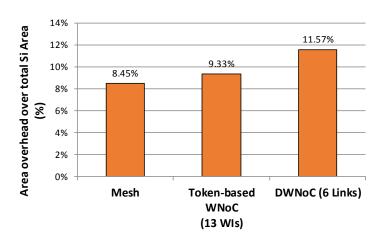

| Figure 4.18 Percentage of area overhead over total silicon area                     | 97           |

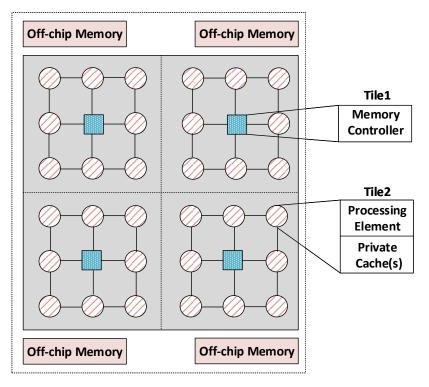

| Figure 5.1 An example of 6×6 Mesh NoC topology with memory controller,              | processing   |

| elements and Off-chip memory                                                        | 100          |

| Figure 5.2 Proposed router architecture                                             | 103          |

| Figure 5.3 The pipeline stages :(a) 5-stage baseline router for packet (b) 2-stages | s for circui |

| switching                                                                           | 105          |

| Figure 5.4 Intermediate steps represent for packet transfer                         | 106          |

| Figure 5.5 PMC controls the inactive/active components                              | 108          |

| Figure 5.6 Optimal memory controller placement using mean-shift approach            | 111          |

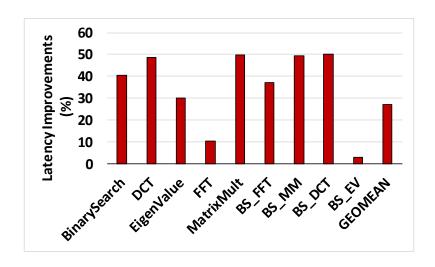

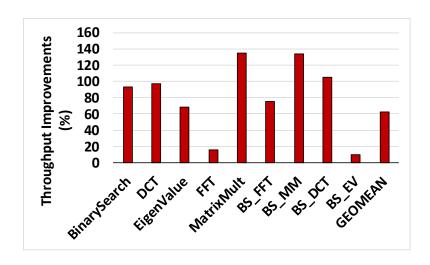

| Figure 5.7 Reduction in memory latency over baseline                                | 112          |

| Figure 5.8 Improvement in peak throughput over baseline                             | 112          |

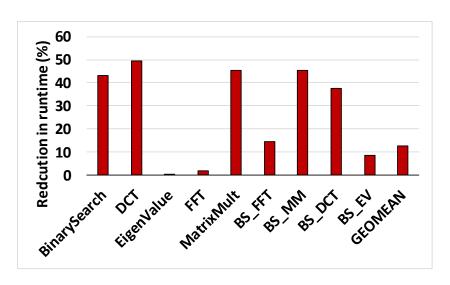

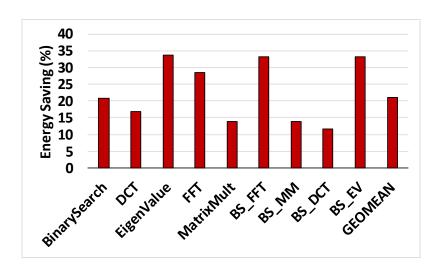

| Figure 5.9 Improvement in application runtime over baseline                         | 113          |

| Figure 5.10 Reduction in network energy over baseline                               | 114          |

# List of Tables

| Table 2.1 Shows the seamless bypass routing strategy                         | 25          |

|------------------------------------------------------------------------------|-------------|

| Table 2.2 Simulation Setup for Proposed NoC                                  | 29          |

| Table 2.3 SPLASH-2 and PARSEC Benchmark Characteristics for Expected T       | rends 35    |

| Table 2.4 Summary of proposed and energy-efficient NoC Architectures         | 36          |

| Table 2.5 Characteristics Table of Proposed NoC                              | 37          |

| Table 3.1 Probabilistic Notations                                            | 44          |

| Table 3.2 Shows AMS Controller mechanism on routers                          | 47          |

| Table 3.3 Shows AMS Controller mechanism on routers                          | 49          |

| Table 3.4 Characteristics of Voltage Regulator                               | 54          |

| Table 3.6 Simulation Setup                                                   | 56          |

| Table 3.5 Representation of Topologies/Components                            | 57          |

| Table 3.7 Router Implementation                                              | 58          |

| Table 3.8 Summary of Existing and Proposed Power/Energy-efficient NoC Ar     | chitectures |

|                                                                              | 64          |

| Table 4.1 Dimensions of the antenna                                          | 74          |

| Table 4.2 Percentage of busy and idle cycles in a 64-core system given defau | ılt problem |

| sizes                                                                        | 95          |

| Table 5.1 Shows algorithm for circuit switching setup                        | 104         |

| Table 5.2 Intensity Classification of PARSEC Benchmark                       | 104         |

| Table 5.3 Shows selection logic for hybrid switching                         | 105         |

| Table 5.4 Simulation setup                                                   | 110         |

| Table 5.5 Summary of Existing and Proposed Works                             | 115         |

### Chapter 1

### Introduction

### 1.1 Motivation and Introduction

The advancements in chip design indicate that there will be a manifold increase in the number of cores on a single die over the next few years. Chip Multi-Processors (CMPs) are gaining significant interest for a wide range of applications; consumer electronics, single-chip cloud computers, supercomputers, defense applications, etc. Intel has recently developed the Knights Landing processor with 36 tiles for high performance computing [1]. A processor array containing 1000 independent processor is fabricated in 32-nm technology node [2]. Other companies like Tilera, Nvidia, and Samsung are also developing the multi-core systems. However, existing methods of integrating and designing multi-core chips do not scale to very large core counts due to several challenges. On-chip communication and power consumption are two such major challenges.

For more than four decades, Moore's Law and Dennard scaling have resulted in increasing transistor integration capacity with a constant power density [3]. With the feature size below 65nm, this trend can no longer be continued from generation to generation, because of exponential growth of leakage current, and limitations of threshold and operating voltage scaling. Recent studies have highlighted the bottlenecks of interconnect power in the total chip power consumption [4]. With CMPs becoming more communication centric as opposed to computation centric, interconnect power plays a key role in accommodating the expected growth in number of cores. These facts emphasize the need to introduce aggressive power saving methods for interconnection networks to achieve an energy efficient CMPs without significant performance degradation.

These can be addressed by introducing a power-aware Network-on-Chip (NoC) that has emerged as the communication platform that enables partitioning of the design effort [5]. Advances in NoC have made it the preferred choice for the communication backbone

of Chip Multi-Processors. However, traditional NoCs suffer from the limitations arising out of a multi-hop communication of conventional planar metal interconnects, where data transfer across the NoC fabric causes high latency and power consumption. With a further increase in the number of cores on a chip, this problem will be significantly aggravated. Several attempts have been made to alleviate the limitations of regular NoC architectures by innovations in routing and interconnect deployments [6]. However, due to the basic interconnect technology being the metal/dielectric combination the performance improvements were only incremental.

Different approaches have been explored to address the limitations of conventional NoCs; such as 3D and Photonic NoCs and NoC architectures with multi-band RF interconnects [7] [8] [9]. All these new technologies are capable of improving the speed and power dissipation in data transfer in a many-core chip. However, in 3D NoCs, manufacturing issues and temperature due to increased power density put a ceiling on the overall performance advantages. Photonic NoCs need an underlying electrical network to set up path and routing information adding to the overhead. RF interconnects based NoCs need laying long on-chip transmission lines across the chip. In comparison, wireless transmission for on-chip data transfer over relatively long distances stands out as a revolutionary alternative which besides improving the performance profiles of modern NoCs, also eliminates the need to lay out waveguides on the chip [10] [11] [12] [13]. Establishing long-range, single hop communication links with wireless transceivers reduces the number of hops involved in data transmission across distant nodes on the chip thus improving performance. Depending upon the operating frequency range the data bandwidth of such links can be very high. Such high bandwidth, low latency long distance links enable the design of novel NoC architectures that were so far impossible to conceive due to age-old limitations imposed by delays along long wires. Of these emerging interconnects, wireless links with mm-wave antennas offer the most feasible solution because of their compatibility with CMOS manufacturing process. Coupled with advances in mm-wave transceiver design [14], on-chip wireless links offer the most promising solution to improve the performance of NoCs. Many Wireless NoC (WNoC) architectures [11] [12] [13] have been proposed with varying performance improvements and overheads. All these different architectures augment conventional wired topology with Wireless

Interfaces (WIs); WIs primarily used for long range communication to reduce multi-hop communications. The advancements made in NoCs and on-chip WIs provide high-performance communication infrastructures to match the computation capabilities of processing elements in many core systems. But, wireless transceivers have their own power overheads, which is another major concern in WNoC architectures.

Most of the wireless NoC architectures are based on omnidirectional antennas. In most cases, these WNoC architectures adopt a token passing based medium access mechanism to transmit data over the shared wireless channel. Since all antennas share a common channel, only a single communication is possible at any instant of time. This limits the performance benefits of using wireless links. One potential solution to achieve simultaneous communications is to have multiple non-overlapping wireless channels. But creating multiple transceivers tuned to non-overlapping channels is an extremely challenging job due to effects of interference. Interference reduces available bandwidth and degrades the bit error rate (BER). The cumulative impact of these leads to poor Quality-of-Service (QoS).

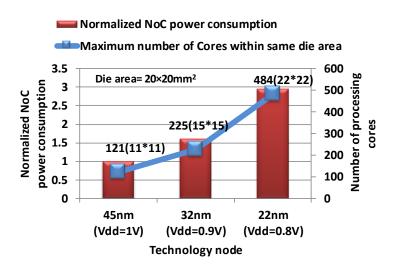

To address these aforementioned issues, we discuss multiple effective solutions to make an efficient communication infrastructure for CMPs. However, as technology scales, interconnect power and latency increases. This results in high power consumption in NoC/WNoC topologies at deep submicron technologies and large system sizes. To realize energy-efficient high-performance computing, it is necessary to introduce aggressive power saving methods for NoCs. The work proposed in this dissertation tackles power consumption in NoC elements to achieve energy-efficient on-chip interconnection in CMPs. The total power consumption in NoC at different technology nodes with different system sizes is shown in Figure 1.1. The network and core power values are obtained using DSENT [15] and McPAT [16] tools. At all technologies, the total die area is kept constant, and power consumption in NoC for given system size is computed. As can be observed, NoC power increases exponentially with technology nodes and increasing system size, though the supply voltage reduces.

Power consumption in network components remains a major issue in deep submicron

Figure 1.1 Normalized NoC power consumption with processing cores at different technology nodes

technology. As CMOS scaling progresses into smaller technology nodes, power has become the primary design constraint. NoC, with many routers transferring data simultaneously, consumes high power and a significant portion of total chip's power. For example, NoC in Intel Teraflop processor consumes 28% of the total tile power [17]. As system size increases, this is further multiplied by several folds with a significantly high number of active routers. In addition to this, it has been shown that it is not possible to operate all system resources (cores, NoC, memory, etc.) simultaneously at full power all the time while meeting Thermal Design Power (TDP) constraints [18]. High power consumption also leads to higher system temperatures affecting the reliability of the system. This makes it necessary to reduce the power consumption in NoC routers for

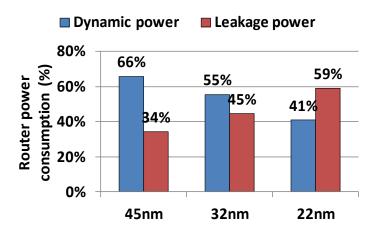

Figure 1.2 Dynamic and leakage power of router at Vdd=1V

energy efficient and reliable system while achieving the required network performance. Figure 1.2 shows the trend of router dynamic and leakage power across different technology nodes from 45nm to 22nm. The results are obtained by simulating a regular router using DSENT [15] and breaking down the power consumption into dynamic and leakage components. Leakage power, unlike dynamic power, increases as technology scales and accounts for 59% of total power at 22nm. This trend shows basically the both leakage and dynamic power consumption is a major concern in NoC architecture. These facts emphasize the need to introduce aggressive power saving methods for NoC router components and aim for energy efficient and reliable interconnection in sustainable computing platforms.

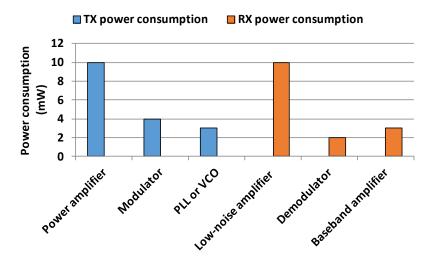

Similarly, power consumption in Wireless Interfaces (WIs), consumed during idle phases of wireless communication, acts as a key energy waste in WNoCs. The component-wise breakdown of WI power, in Figure 1.3 [19], shows that WIs dissipate high power; and Low-Noise Amplifier (LNA) and Power Amplifier (PA) consume most of it. The energy efficiency at routers as well as WIs has become a major issue for NoC architecture. The power consumption in baseline router and idle-state power dissipation in WIs has to be reduced to achieve low power on-chip communication while providing desired network performance.

Based on this utilization of routers, we propose a leakage power-aware NoC architecture to reduce the power consumption using power gating strategy. The methods of

Figure 1.3 Component wise power consumption of transceiver at 65nm

router utilization computation are discussed in chapter 2. Due to presence of power gated routers, packets may drop or packet latency may increase by storing the data into virtual channels. Therefore, it is also essential to reduce the packet drops and latency to avoid the performance degradation. To maintain the performance, we propose a seamless bypass routing strategy which helps to route the packet by bypassing the power gated router(s) as well as reduce the packet drops.

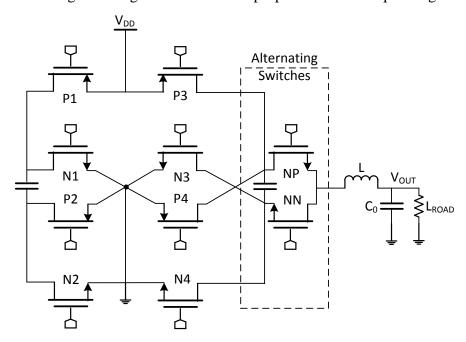

In order to achieve energy-efficient communication, we propose switching power-aware WNoC using Adaptive Multi-Voltage Scaling (AMS) control technique for wired and wireless NoC architectures. The AMS mechanism follows a hybrid approach to implement voltage scaling in router components and power gating in WIs to save switching and idle-state power respectively. It operates based on utilization of components during different application activity phases to adaptively vary supply voltage and reduce energy consumption in NoCs. The utilization of router components is computed using precomputed global utilization and stochastic router utilization models that are discussed in section 2.2 (Chapter 2) and 3.2 (Chapter 3) respectively. The stochastic utilization model is derived dynamically by observing routing characteristics of the application at each router. The stochastic modeling of router utilization allows AMS to adapt to different applications according to their performance requirements while maintaining optimal network power consumption.

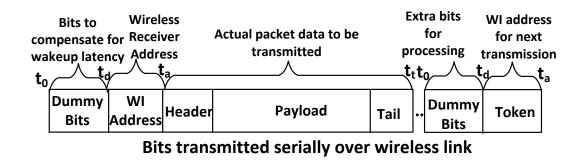

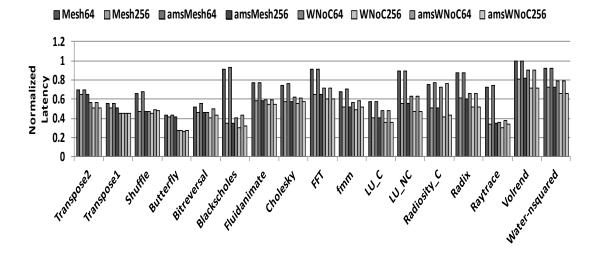

At the same time, we also evaluate the utilization of WIs to increase the energy-efficiency of WNoC. WI utilization is tracked by verifying availability of token and data to be transmitted at each WI and power gating them when they are not actively engaged in communication. As token is transmitted through wirelessly, in this case, token can be missed due to inactive receiver-end. To receive the token by waking up periodically is not a feasible solution due to excessive transient energy overhead. This is one of the major challenge in power gated WIs. To avoid this, we propose a sophisticated receiver-end wake-up control strategy using address signature along with data packets. This strategy processes the signature without interrupting the inactive components. For this, the unique signature of desired receiver WI is appended between dummy bits and actual packet data to be transmitted. We add a certain number of dummy bits with the original packet to avoid data loss during signature matching and wake up latency. We ensure that the extra dummy

bits added with the original data introduces minimal overhead. At the receiving WI, the received bits are decoded for this WI address using a pattern matching decoder. If the address matches, remaining actual data is received. If there is a mismatch, packet reception is ceased and LNA is put back to sleep state. The pattern matching decoder is operated at serial data stream frequency and starts decoding WI address after LNA is active.

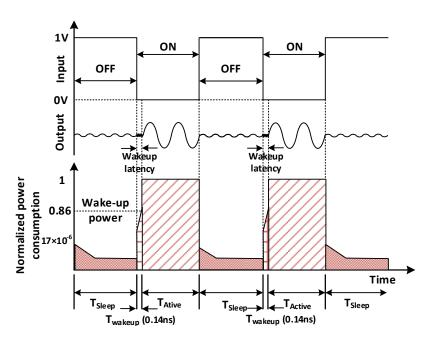

In order to improve performance and avoid limitations of existing single channel WNoCs, we also propose a Directional Wireless NoC (DWNoC) architecture using Planar Log-Periodic Antennas (PLPAs) in this dissertation. In this topology, we propose an interference-aware wireless nodes placement algorithm to improve the performance. To achieve that we define constraints that can result in wireless interference and find placement that avoids all such constraints. This will enable us to create multiple concurrent wireless links eventually improving performance and energy-efficiency. We explore the PLPAs for the on-chip wireless links and demonstrate the use of their directivity to enable pair-wise communications. We present Directional Wireless NoC (DWNoC) architecture following three requirements: interference-avoidance, low power dissipation and performance enhancement through concurrent links.

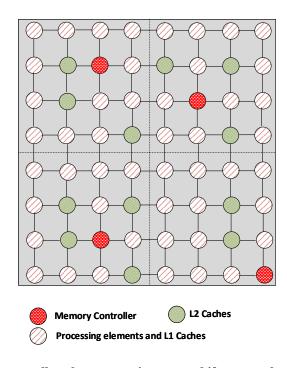

In addition, communication between LLC and memory controllers faces significant challenge due to the placement of memory controllers, high network latency, and switching strategy. Though advancements like multichannel memory controllers, High Bandwidth Memory (HBM) etc. improve memory bandwidth; limited number of pins restricts the total number of memory controllers. With few memory controllers servicing requests from large set of cores, placement and interconnections of these memory controllers within NoC play a significant role in providing efficient off-chip memory access. Several works in the past have demonstrated the capabilities of NoC to provide high-performance communication in CMPs. Intel's 80-core [17] design arranges cores in 10x8 2D mesh network with 5-port routers and provides a bandwidth of 80Gbps per tile. Tile64 from Tilera [20] uses 8x8 2D mesh and provides a bisection bandwidth of 2.56Tbps. Both these architectures use memory controllers placed at top and bottom of the network. With fewer number of memory controllers, better NoC design and placement can have a huge impact on system performance. Arbitration policies between memory requests arriving at each memory controllers have been proposed in [21] [22] to provide better interconnection support for

improving memory performance. A memory controller placement and routing between cores and memory in [23] have shown that diamond placement with 16 memory controllers provides optimal performance in 8x8 mesh based CMP. A generic placement method with divide and conquer approach [24] analyzes different memory controller placements based on hop count metric. NoC hardware supports have also been explored to provide high bandwidth off-chip memory access. Another possible solution to provide high bandwidth memory access is to establish dedicated paths between processing elements and memory controllers. But, this is not scalable with increasing system sizes.

In order to improve the performance of memory accesses in CMPs, we introduce an adaptive hybrid switching strategy, which is a combination of circuit switching and packet switching strategy, with dual crossbar router. As studies show that optimal placement of memory controllers can optimize the communication mismatch significantly, so, we place the memory controllers to enhance the memory Bandwidth. To reduce the energy overhead of dual crossbar routers, we present partially drowsy and power gating techniques in the proposed architecture.

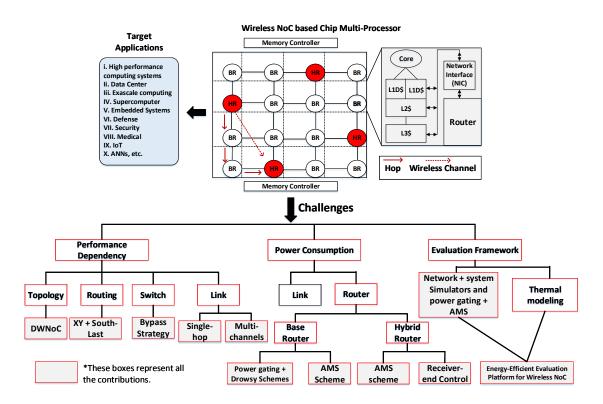

#### 1.2 Contributions

The overall contributions of this thesis are illustrated in Figure 1.4. This figure highlights the target applications, WNoC based CMP and associated challenges. Hybrid NoC architecture consists of a large number of tiles. The contents of this tile are a router, core, caches (L1, L2, and L3), network interface controller and links (hop). There are two types of routers such as base router (BR) and hybrid router (HR). Each tile is connected to neighbor routers through links. Packets are transmitted from one core to another through links and routers. If there are multi-hop communications, packet adopts the wireless links depending upon the availability of wireless channel and token passing Medium Access Control (MAC) protocol. The main challenges associated with this interconnect technology are performance dependency, power consumption due to NoC components and evaluation framework for WNoC. Our main contributions in this thesis are presented by shaded boxes, those are discussed one by one in the following sections.

Figure 1.4 Overview of energy-efficient WNoC highlighting all the Contributions

The major contributions of this work are as follows:

- I. A low power router architecture using partially power gated router coupled with drowsy VCs is proposed to reduce leakage power based on the router utilization as discussed in Chapter 2. To reduce the impact on performance of the proposed power saving methods, we introduce a Low overhead, deadlock-free seamless bypass routing strategy. We evaluated the power and area overheads along with impacts of power gating. We also did a detailed comparative analysis of the proposed techniques with the state-of-art.

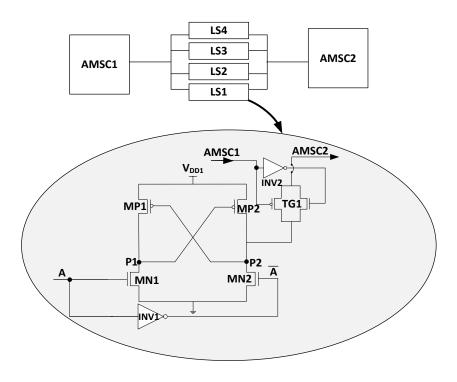

- II. We propose a low overhead adaptive two-step hybrid estimation method using stochastic process for router utilization from its past usage pattern. Based on the utilization of routers, we propose an energy-efficient NoC architecture using Adaptive Multi-Voltage Scaling (AMS) mechanism to achieve significant energy saving by scaling the voltage of router components as discussed in Chapter 3. To implement the AMS scheme with NoC, a multi-level voltage shifter that allows switching between two voltage levels from a given fixed set of voltage levels. We also integrate on-chip

voltage regulator and level shifter with routers. We also use power gating enabled WIs using AMS to reduce the idle-state power dissipation and in that process significantly improve power efficiency of the NoC infrastructure.

- III. For packets transmitted over wireless links, a receiver-end control strategy is proposed to wake up the desired receiver based on token as discussed in Chapter 3. This scheme proposes to use unique address signature along with data packets. The inactive components will remain so until signature matches by pattern matching decoder at the desired WI. This enables effective power gating strategy for WIs as it eliminates periodic waking up of complete receiver chain. This signature is appended between dummy bits and data packet. These dummy bits are appended with packet to avoid the data lost due to components in inactive mode. The proposed technique also reduces routing overhead and need of control signals significantly.

- IV. A DWNoC architecture using PLPA antenna is explored for multichannel simultaneous communications without interference as discussed in Chapter 4. Simultaneous communication can enhance the overall system performance significantly. We propose the interference-aware WIs placement algorithm and routing strategy for minimizing interference effects. This algorithm also helps in the optimal utilization of the WIs and increases the energy-efficiency of the network compared to the WNoC setup with omnidirectional antennas.

- V. To enhance the performance of the system in terms of memory access latency, we propose an energy-efficient adaptive hybrid switching strategy with dual crossbar routers that allow simultaneous use of both circuit and packet switched paths as discussed in Chapter 5. An optimal number and placement of memory controllers in the network using machine learning approach are also introduced to increase the memory access bandwidth. A routing protocol for seamless communication between last level caches and memory controllers using adaptive hybrid switching strategy is also proposed.

VI. We developed a performance evaluation framework using system and network simulators for WNoC. Router utilization based metric is introduced and is applied to enable design and evaluation of energy-efficient architecture by implementing AMS with power gating. The proposed framework is implemented on top of an existing cycle-accurate open-source network simulator and system simulator. The framework is used for experimental evaluations under various application-specific and synthetic traffic scenarios to validate our proposed works.

### 1.3 Dissertation outline

The remaining of this dissertation is divided into 5 chapters. In this section, we discuss the contents each chapter briefly.

Chapter 2: We implement the leakage power aware NoC architecture with power management controller to apply fine-grained power gating in NoC routers based on the utilization of the routers. The utilization computation method for routers is discussed in this chapter. The design of router bypass links and control circuitry is presented to transfer data through power gated routers. A deadlock-free seamless bypass routing is presented that makes use of bypass links to minimize the adverse effects of power gating and maintain performance. A walk-through example describes the various steps involved in power gating and routing data in NoC under various possible scenarios. We also present a detailed analysis of power and area overheads of proposed architecture, impacts of power gating and comparison of proposed design with existing low power techniques.

Chapter 3: First, a detailed description of dynamic runtime utilization computation for estimating router utilization with low runtime overhead is presented. A stochastic model is developed for accurate prediction of router utilization from its past utilization characteristics during dynamic runtime utilization computation phase. The supply voltage of router elements is varied dynamically based on the predicted utilization. To reduce the switching power, AMS control mechanism, implemented to reduce switching power in router elements and idle-state power in WI components is described in this chapter. Similarly, we power gate the WI components, when they are not actively involved in data

transmission to reduce idle-state power consumption. We present the details of AMS controller, along with multi-level voltage shifter and voltage regulator to dynamically change supply voltage of router components and WIs based on their utilization and save network energy. A control mechanism for packet transferred over wireless link is presented to avoid the data loss and maintain the signal fidelity in the presence of power gated WIs. A new approach to transmitting medium access token through wireless link is proposed to minimize control signal latency. A detailed discussion and analysis of the impact of PVT variations of PA and LNA are discussed in results section.

Chapter 4: We demonstrate directional antenna based WIs for interference-aware DWNoC architecture for many-core systems to overcome the bottleneck of existing WNoC setup with omnidirectional antennas. It is also shown that DWNoC can establish concurrent links which do not interfere with each other. Simultaneous communications can enhance the overall system performance significantly. We also propose the interference-aware WIs placement algorithm and routing strategy for minimizing interference effects. This algorithm also helps in the optimal utilization of the WIs in the network with minimum overheads.

Chapter 5: In this chapter, we highlight the on-chip communication bottlenecks between Last Level Caches (LLC) and Memory Controllers (MCs) to access off-chip memory. To overcome this, we discuss hybrid switching strategy with dual crossbar routers that allow simultaneous use of both circuit and packet switch paths. We also try to find the optimal number and placement of memory controllers in the network using machine learning approach. We further improve upon this by using power-efficient drowsy virtual channels and power gating techniques to achieve energy-efficient off-chip memory access. A routing protocol is introduced for seamless communication between LLCs and MCs using adaptive hybrid switching strategy.

**Chapter 6:** In the last chapter of this dissertation, we conclude our present research work with detailed outcome and future research directions in the domain of efficient communication infrastructure.

### Chapter 2

## Leakage Power-aware NoC

In this chapter, we implement the leakage power aware NoC architecture with power management controller to apply fine-grained power gating in NoC routers based on the utilization of the routers. The utilization computation method for routers is discussed in this chapter. The design of router bypass links and control circuitry is presented to transfer data through power gated routers. A deadlock-free seamless bypass routing is presented that makes use of bypass links to minimize the adverse effects of power gating and maintain performance. A walk-through example describes the various steps involved in power gating and routing data in NoC under various possible scenarios. We also present a detailed analysis of power and area overheads of proposed architecture, impacts of power gating and comparison of proposed design with existing low power techniques.

We tackle the leakage power consumption in NoCs and propose ways to reduce the leakage power without impacting the performance. Analysis of router power consumption shows that leakage power accounts for a significant portion of total NoC power. We also notice that the contribution of leakage power increases with technology node, specifically in deep-submicron nodes. We reduce the leakage power consumption using power gating in base router. Power gating operation in NoC architecture is implemented using router utilization data. Router utilization is estimated in two steps: i) Pre-computed global utilization and ii) Run-time utilization. In this chapter, we implement a cost-effective runtime utilization estimation method to save the leakage power. In the first step, utilization is pre-computed from the knowledge of hardware and the application characteristics. This pre-computation provides a coarse utilization estimate and helps us to identify routers that are at the extreme ends of utilization i.e., very highly used or rarely used. The runtime utilization estimation is performed on remaining routers and provides a fine estimate to capture router idle phases during application execution. The two-step hybrid approach helps us in achieving the most accurate profiling of router utilization characteristics and

maximizing energy savings while reducing the estimation overheads.

In this work, we propose leakage power and performance-aware NoC architecture using power gating technique to achieve energy-efficient communication in many core systems. Of all router components, leakage power consumption in crossbar fabric and virtual channels is comparatively high [18]. Hence, the proposed method partially power gates the router to turn off these components that account for most of the leakage power in NoC. Power gating techniques, in general, have performance penalty due to associated wake-up latency in bringing a circuit to the active state. Similarly, it can have performance or energy penalties due to 1) short-term sleep periods within high cumulative utilization phase; 2) wake-up due to burst traffic during light utilization; 3) blockage of paths and 4) isolation of routers. To overcome these effects, we propose a Seamless Bypass Routing (SBR) strategy. SBR uses bypass links to route data through power gated routers effectively. It reduces the impacts of wake-up latency, congestion, blocking and isolation due to power gated routers and minimizes the impacts of power gating on communication performance. Using power gating, NoC allows for static reconfiguration of NoC according to the application requirements and reduces power consumption. By considering runtime utilization locally at each router, further reduction in leakage power consumption in router is achieved.

### 2.1 Related work

Communication performance over long distances and power consumption have been major challenges for many-core NoC architectures. WNoC architectures like the ones proposed in [11] [12] [13] [14] [25] [26] by inserting low latency and low energy wireless links, improve performance over traditional wired only NoCs. With power becoming major design constraint in ultra DSM technologies, several low power design techniques like dynamic scaling, multi  $V_t$  cells, clock/power gating, etc. [27] have been proposed to reduce power consumption in CMOS ICs. Recently, several works have explored implementing such methods to reduce power consumption in links/routers and achieve energy efficient network infrastructures.

Power gating schemes, that cut-off power supply to a circuit when it is not active,

have been widely used for leakage power reduction and also been employed for NoCs [28] [29] [30]. Panthre [31], a power-aware routing and topology reconfiguration method is proposed to provide long uninterrupted intervals of sleep to selected units using power gating. Panthre considers link utilization to implement power gating and if utilization of a datapath is below predefined threshold, it is put in sleep state. Ultra fine-grained run-time power gating method for on-chip routers is proposed in [32] that reduces leakage power using look-ahead technique but with performance penalty. Fine-grained power-gated FlexiBuffer that reduces buffer leakage power is proposed in [33], and can operate with minimal changes to flow control. NoRD (Node-Router Decoupling) [34] is a novel technique for power gating bypass, that decouples the Node's ability of transferring packet by monitoring the status of associated router. Traffic based virtual channel activation is explored in [35] for low power applications. Power Punch, a novel performance aware technique has been proposed to achieve non-blocking power gating of on-chip routers [36]. In this paper power control signal is sent ahead of the packet to punch-through any blocked routers along the imminent path of packets. An energy efficient virtual channel power gating mechanism is discussed in [37] for on-chip networks to save the leakage power. All these schemes offer leakage power savings using efficient algorithms based on link/virtual channel/application utilization. Many of these algorithms either depend on predetermined router/link utilization estimation or perform completely runtime utilization estimate. Predetermined utilization estimates can be obtained with reduced overheads, but offers minimal flexibility that can adversely affect performance. On the other hand, fully runtime estimation methods offer dynamic control options but require significant overheads.

To maximize leakage power saving in NoCs with minimal overheads, we propose a hybrid utilization estimation approach, NoC in this work. The two-step utilization computation finds a good balance between rigidity of predetermined methods and runtime overheads. The pre-computed estimate reduces the number of routers controlled dynamically at runtime, limiting the estimation overheads. On the other hand, runtime utilization estimate captures the detailed activity characteristics during different phases of application execution to maximize energy savings. In addition to this, NoC promises to increase power efficiency of on-chip wireless communication significantly along with regular router components. A flow control technique that allows packets to bypass router

pipeline stages [38]. ShortPath is augmented with a fine-grained pipeline bypassing mechanism to skip all the stages without contention for high speed applications [39]. Authors in [40] combine two techniques of adaptive channel buffer and router pipeline bypassing to simultaneously reduce power consumption and improve performance. An evaluation of bypassing technique is discussed based on traffic by avoiding the full routing functionality of selected nodes [41]. Single-cycle Multi-Hop Asynchronous Repeated Traversal (SMART) is proposed to dynamically set up single-cycle paths with turns from source to destination [42]. A Seamless bypass routing strategy proposed along with power gating control minimizes the performance impacts and adverse effects of power gated routers in the network. We present a detailed discussion of NoC architecture and performance evaluation of NoC architecture with WNoC. We explore performance overhead and associated trade-offs for realizing the proposed framework.

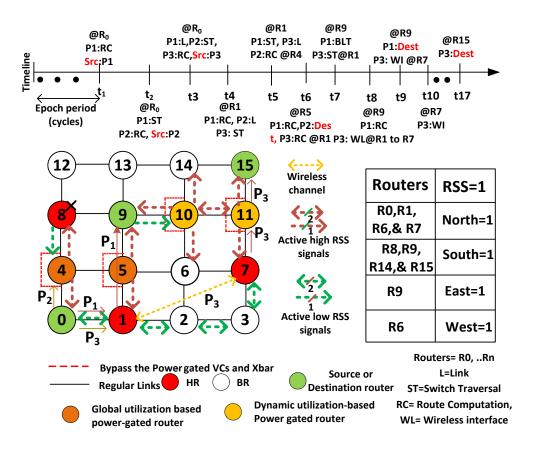

### 2.2 Leakage Power-Aware NoC

A generic NoC architecture consists of routers attached to message source/sink components; with all routers interconnected by wires in a specific topology. WNoC architectures, using strategically and optimally placed WIs at some routers, provide long distance wireless communication to improve NoC performance. A WNoC topology, with Base Routers (BRs) and Hybrid Routers (HRs) (BR + WI) is explored in [43] [44]. In this section, we discuss the hybrid two-level utilization estimation based power gating strategy and router design implemented in proposed architecture. We describe the power management controller that decides router power gating operation and router modifications necessary to reduce NoC leakage power consumption without effecting performance significantly.

#### 2.2.1 NoC Router Design

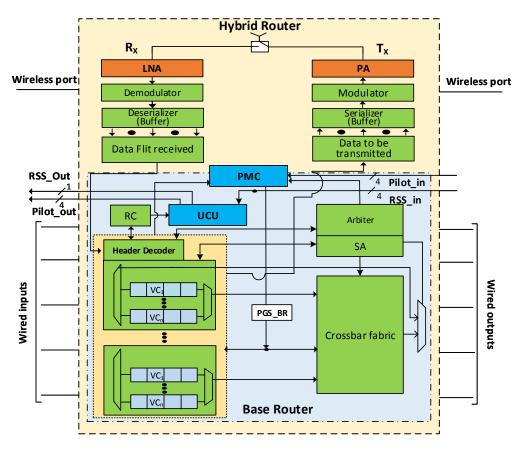

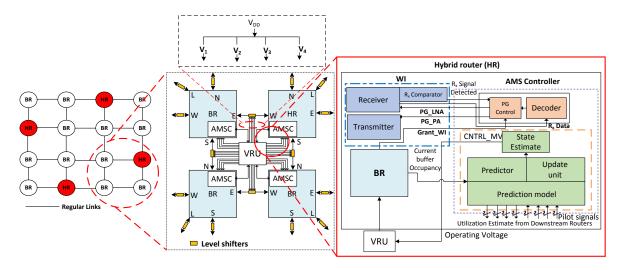

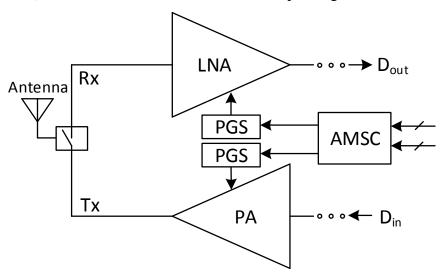

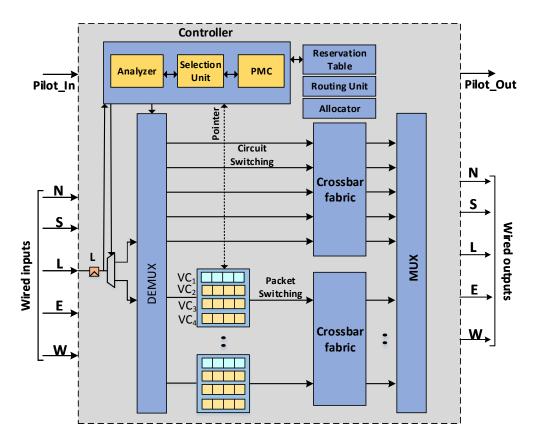

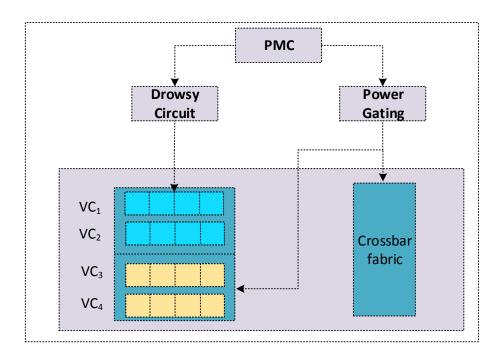

The architecture of power gated router design implemented in NoC is shown in Figure 2.1. The BR components of NoC router are typical of any NoC router design and provide similar functionality. The router design consists of six major components: i) BR components that include wired I/O ports, buffers & virtual channels, crossbar fabric, route computation unit, switch allocation and arbiter, ii) WI components, iii) Utilization

Figure 2.1 Implementation of power gated hybrid router design for proposed NoC

Computation Unit (UCU), iv) Power Management Controller (PMC), and vi) Bypass links and multiplexing circuit. HR, shown in the figure, contains WI components and control signals along with all BR components. WI components include serializer, modulator, Power Amplifier (PA) at the transmitter and Low Noise Amplifier (LNA), demodulator, deserializer at the receiver. A Voltage Controlled Oscillator (VCO) is used to generate the required carrier signal for both transmitter and receiver. These components provide the necessary hardware to read packet data from BR and convert it to analog information that can be transmitted over wireless channel. UCU observes activity of the router and computes runtime router utilization. PMC reads necessary information about the status of router and makes decision about power gating the router. The bypass links with multiplexing circuitry implement SBR strategy to reduce the adverse impacts of power gating and avoid performance penalties in NoC.

#### 2.2.2 Global Utilization Computation

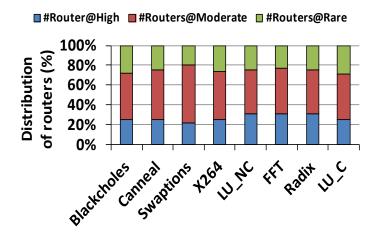

The hybrid approach operates using two levels of router utilization. The coarse grain pre-computed utilization is observed over entire application period and helps us to categorize routers as Highly-Utilized (HU), Moderately-Utilized (MU) and Rarely-Utilized (RU). Each router is placed into one of these three categories based on their precomputed global utilization. The threshold that indicates which category the router belongs to, depends on the application being run on the many-core system. The threshold value for each category is set as less than 10% for RU, utilization between 10% and 75% for MU and HU routers have utilization more than 75%. As the name suggests, routers classified as RU are rarely used over entire application time, whereas HU routers are active for most of the application time. MU routers fall in between these two categories. Figure 2.2 shows the number of routers falling into each category for different PARSEC [45] and SPLASH-2 [46] benchmarks. It can be seen that less than 30% of routers are highly active across all benchmarks simulated and on average 48% of routers are moderately utilized. This allows us to save power consumption in routers with low utilization by reducing their voltage without impacting performance significantly. The utilization of the routers may vary with application to application. We define thresholds for router categorization based on precomputed router utilization as shown in Figure 2.2 to reduce the hardware overheads. Thresholds are estimated by running the *PARSEC* and *SPLASH-2* benchmarks suite. In our

Figure 2.2 Categorization of routers based on pre-computed global utilization under real applications for a 64-core system

simulation setup, we run the applications individually to estimate the thresholds. These utilization thresholds may change with other benchmarks or multiple simultaneous applications. For such cases, the thresholds and number of routers falling into each category vary according to those application/s characteristics. But, NoC architecture can be reconfigured by setting new threshold values without any changes.

For estimating the router utilization at global level in our experiments, a counter is associated with each router and is incremented whenever routing decision for that router is made. All counters are reset at the start of simulation. A total count is computed from the sum of individual counts of all routers. The utilization of any router is given by the ratio of a router's count and the total count. Therefore, at any cycle, utilization of the desired router can be observed. Utilization of router,  $U_r$  can be determined as,

$$\operatorname{Ur}_{i} \Big|_{t} = \left(\frac{Rc_{i}}{\sum_{i=1}^{n-1} Rc_{i}} \times 100\%\right)\Big|_{t},$$

Where  $Ur_i$  is the utilization of  $i^{th}$  router,  $Rc_i$  is the register count of the  $i^{th}$  router, n is the total number of routers and t is the given simulation cycle time at which function call is being made. Given the dynamic nature of the metric, time (t), is only used for reference purposes. In the following subsection, we discuss the runtime utilization estimation method of MU routers.

#### 2.2.3 Runtime Utilization Estimation

To achieve maximum leakage energy saving with minimal runtime overheads, proposed NoC architecture estimates router utilization in two steps. During the precomputation step, UCU estimates the utilization of a router for the entire application period. We implement this using proposed NoC, where each router can be power gated individually using a power management controller. In the proposed method, routers under RU are power gated throughout the application. Routers under HU are never power gated. Finally, MU routers are power gated dynamically based on run-time utilization estimate. This reduces the runtime computation overheads of power gating operation in proposed NoC.

To achieve better power efficiency in MU routers, proposed NoC exploits runtime utilization of a router during different phases of the application execution. The runtime utilization estimate of MU routers is computed on an epoch-to-epoch basis at the start of each epoch. An epoch signifies a fixed/variable duration phase in total simulation period. An epoch's duration can remain fixed throughout the application or varied for each epoch and duration is determined to suit application needs. For our simulations, we have used fixed duration of 1K cycles for each epoch. The value is chosen empirically for the set of benchmarks used in our simulations. The longer epoch durations do not provide the necessary granularity to capture different application phases, while smaller durations increase runtime overheads of control operations. The utilization estimate is computed as the number of cycles for which the router is active within an epoch period. UCU in each router computes runtime utilization for all neighboring routers that are at one hop distance from it. At the start of an epoch, it processes the packet headers that are waiting in its input VCs through Header Decoder (HD) to determine the number of packets that will be routed to each output port. If the numbers of packets that are to be transferred to an output port are less than a predetermined global threshold, UCU sets the downstream router connected to that port to be underutilized for the next epoch. Once UCU completes its operation, the utilization estimate information of neighboring routers is transferred to each corresponding router.

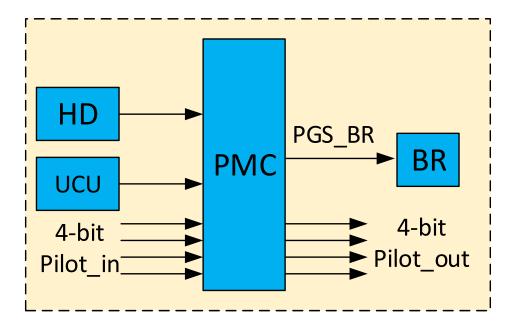

## 2.2.4 Power Management Controller (PMC)

Power Management Controller (PMC) of NoC controls the power gating operation of router components and generates the necessary power gating control signal such as  $PGS\_BR$  for base router components as presented in Figure 2.3. An active high PGS signal from PMC indicates that corresponding components need to be power gated and vice-versa. At the start of each epoch, PMC receives its runtime utilization estimate from all neighboring routers as 1-bit  $Pilot\_in$  signals. It also transmits the results of UCU as  $Pilot\_out$  signals; one 1-bit  $Pilot\_out$  for each neighboring router. An active high pilot signal indicates the utilization is low. In a simple mesh, PMC sends four  $Pilot\_out$  signals and receives four  $Pilot\_in$  signals from neighboring routers.

In BR, VCs and crossbar consume significant portion of leakage power and hence

Figure 2.3 Block level diagram shows power management controller with control signals

only these components are power gated i.e., routers in NoC are partially power gated. PMC utilizes pre-computed and runtime router utilization estimates to generate PGS\_BR signal and control power gating operation. Routers falling under HU/RU categories are never/always power gated respectively throughout the application period. PMC in these routers sets PGS BR to be active low/high for HU/RU respectively for entire application period and disables all runtime control operations by UCU. Power gating operation in MU routers is enforced at the start of epoch based on runtime utilization estimates. At the start of each epoch, PMC receives utilization estimates from all neighboring (one-hop distance) routers as *Pilot\_in* signals and makes a decision regarding the enforcement of power gating. If more than half *Pilot\_in* signals indicate that the router is going to be underutilized, PMC power gates the BR components. The VCs and CF of router remain in sleep mode for that entire epoch duration until a new decision is made at the start of next epoch. To communicate the power gating status of the router, a one-bit Router Status Signal (RSS) is transmitted by PMC to all neighboring routers. Active high RSS represents that particular router is power-gated. This is utilized in seamless Bypass Routing Strategy (SBR) strategy by neighboring routers to effectively route the packets through power gated routers. Similar to the *Pilot\_in* signals received from neighboring routers that indicate router's utilization estimate, PMC transmits Pilot\_out signals to all neighboring routers indicating their

runtime utilization estimate as computed by UCU.

While UCU is computing utilization of neighboring routers, the router continues its regular operation. UCU and its operation lie outside the input to output critical path of the router and do not add additional delay to packet transfer. When PMC makes the decision to power gate the router, an active high *PGS\_BR* signal is sent to router components, and an active high *RSS* signal is sent to neighboring routers. Once the router is power gated, bypass links are enabled to transfer packets through the power gated router. When a power gated router is being brought to the active state, PMC wakes up the router components and sends active low RSS to neighboring routers, and the neighboring routers can start routing packets normally.

### 2.2.5 Routing Strategy

The hybrid two-level utilization based approach of NoC reduces leakage power consumption in NoC significantly by selectively power gating the routers. But, turning off some routers in the network can lead to some adverse effects like performance degradation due to wake up latency, congestion, router blocking, deadlock and isolation. To overcome these challenges and reduce the impact of power gating on performance, we propose Seamless Bypass Routing (SBR) strategy that uses bypass links and additional router modifications to effectively route data through partially power gated routers, where only VCs and crossbar fabric are turned off.

### **2.2.5.1 Bypass Links**

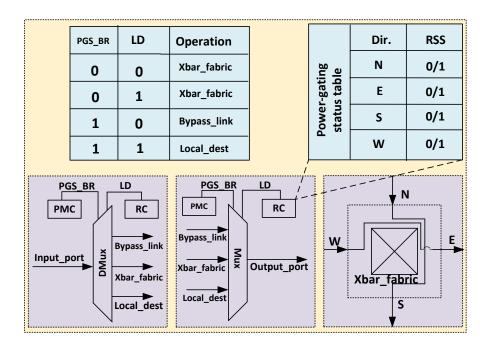

To implement SBR strategy, we add two changes to NoC router architecture compared to regular router design; bypass links that allow data to be transferred through a power gated router and a power gating table with Router Computation (RC) unit, that stores information about power gating status of four neighboring routers as shown in Figure 2.4. The two addition additional bypass links in NoC router connect North & South ports and East & West ports bypassing the crossbar fabric as shown in the figure. These links provide means to transfer data through a power gated router and reduce stalling and re-routing of packets at the neighboring routers. At each input and output port, demultiplexer and multiplexer are added respectively that control the flow of data through either crossbar

Figure 2.4 Router bypasses links and control circuitry

fabric or bypass links. The demultiplexer at the input port is controlled by two signals, power gating signal from PMC and Local Data (*LD*) signal from RC unit. *LD* indicates that destination of the data at the input is local node. When the router is not power gated, data from the port is written to the buffers and transferred through crossbar as in a regular router. When, it is power gated, data is routed either to local port or bypass link according to *LD* signal. At each output port, a multiplexer is added which is again controlled by power gating and *LD* signals. Under regular router operation, data is taken from crossbar fabric. When the router is power gated, data is either taken from bypass link or local port as per the *LD*. To avoid the deadlock, one buffer slot is reserved for RC computation of each VC.

A power gating status table is maintained with RC, which stores information about the status of neighboring routers as shown in Figure 2.4. The entries in the table are updated based on RSS received at the start of epoch. An entry '1' against any port indicates that the router connected to that port is power gated and is used while determining the output port for a packet. The use of bypass links when router is power gated, and SBR strategy to minimize the adverse effects of power gating are explained in subsequent section.

## 2.2.5.2 Seamless Bypass Routing

Performance degradation in NoCs with power gated routers arises from re-routing

Figure 2.5 Pipeline stages of (a) regular XY routing and (b) seamless bypass routing